Please select your location and preferred language where available.

Kioxia, ESSCIRC 2022에서 56-Gbps PAM4 신호를 송수신할 수 있는 트랜시버를 개발

- 2022년 10월 4일

- Kioxia Corporation

Tokyo- 메모리 솔루션의 세계적 선도업체인 Kioxia Corporation은 9월 22일 ESSCIRC 2022(IEEE European Solid-State Circuits Conference 2022)에서 56-Gbps PAM4 신호를 송수신할 수 있는 트랜시버를 개발했다고 발표했습니다.

최근에는 데이터 센터와 같은 더 높은 전송 속도와 용량을 포함하는 네트워크 인프라를 위해 기존의 NRZ 대신 PAM4(다중 레벨 변조 방식 중 하나) 가 고속 통신이 채용되기 시작하고 있습니다. 그러나 PAM4를 사용하면 클럭 복구가 실패할 수 있으며 그 결과 잘못된 클럭 신호로 인해 수신기 성능이 심각하게 저하될 수 있습니다.

이러한 기술적 문제를 해결하기 위해 Kioxia는 클럭 오인식을 회피하는 기술을 개발했습니다. Kioxia는 MEC(모바일 에지 컴퓨팅) 서버용 고대역폭 대용량 메모리 모듈에 이 false-lock-aware 잠금 기술을 적용할 것입니다.

이 개발은 NEDO(New Energy and Industrial Technology Development Organization)에서 의뢰한 프로젝트를 기반으로 합니다.

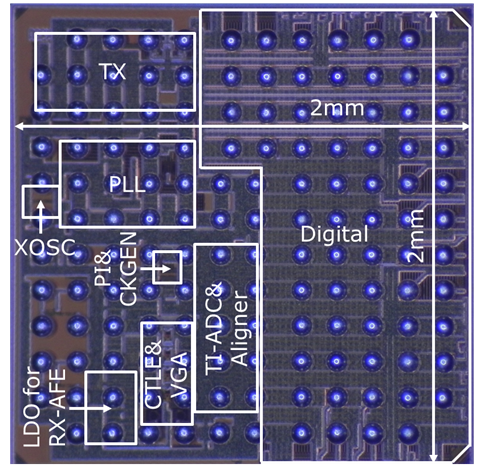

그림 1 16nm-FinFET 기술을 사용한 트랜시버의 칩 현미경 사진. ©2022 IEEE(*7)

1. 개요

최근 5G(5세대 모바일 통신 시스템), IoT 및 기타 기술의 광범위한 채택으로 인해 고속 데이터 통신에 대한 수요가 증가했습니다. 데이터 센터와 같은 네트워크 내 인프라의 전송 속도 및 용량 확장을 위해 기존 NRZ(*2) 대신 다중 레벨 변조 방법 중 하나인 PAM4(*1) 이 사용되기 시작했습니다. 클럭 신호의 속도는 종래의 CDR(*4)회로에 대한 데이터 신호의 변조 속도(*3)의 2배입니다. 그러나 현재 고속 CDR의 소비 전력을 줄이기 위해 클럭 속도가 변조 속도와 동일한 보 레이트 CDR 회로가 사용되고 있습니다. 불행히도, PAM4 수신기에서 전송 속도 CDR을 사용하면 때때로 클럭 복구가 실패하고 수신기의 성능이 심각하게 저하됩니다.

이 문제를 해결하기 위해 NEDO와 Kioxia는 함께 올바른 클럭 복구 기법을 개발했습니다. 먼저, 비교기(*5)는 올바른 클럭 회수를 달성하기 위해 NRZ 모드에서 작동하며, 그 후 비교기는 PAM4 모드로 업데이트됩니다. 56-Gbps PAM4 트랜시버(*6)는 16nm FinFET 기술을 사용하여 제조되며(그림 1), 개발된 기술은 제조된 트랜시버의 측정을 통해 검증됩니다.

Kioxia는 IEEE European Solid-State Circuits Conference 2022(ESSCIRC 2022)에서 이러한 개발을 발표했으며, 이 컨퍼런스는 9월 22일(*7)이탈리아 밀라노에서 개최되었습니다.

2. 성과

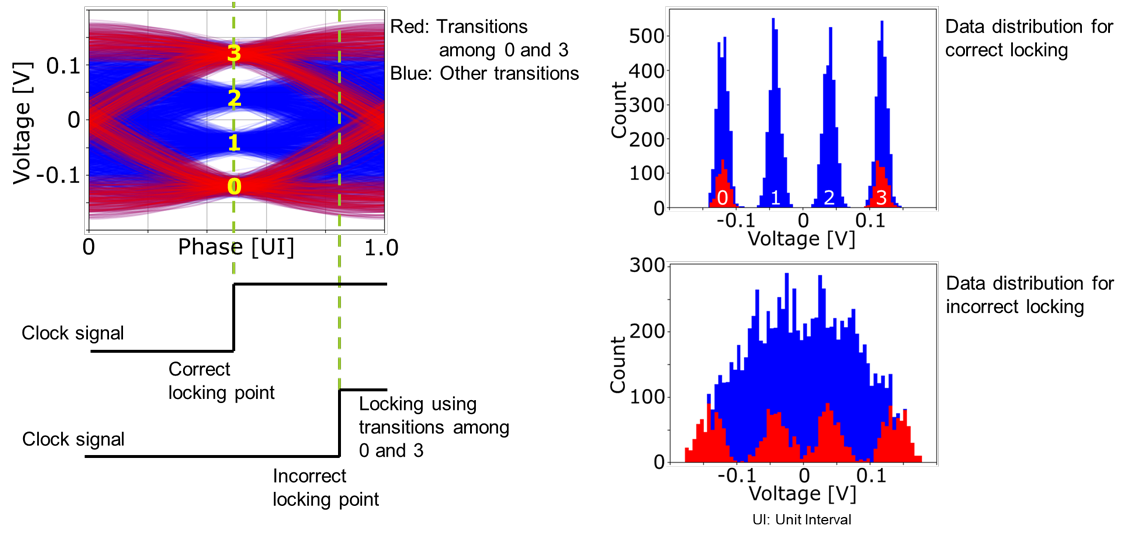

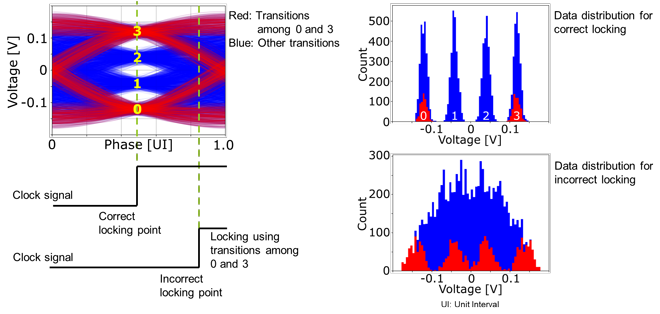

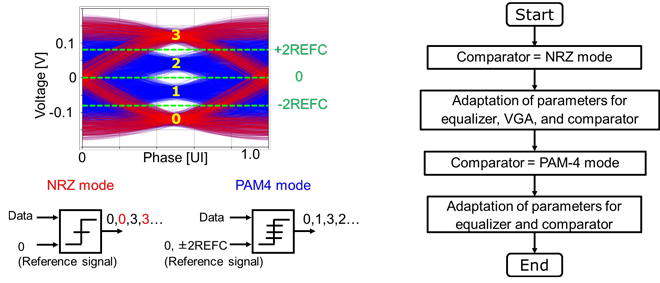

종래의 전송 속도 CDR 회로에서, 클럭 신호는 PAM4 신호의 전체 전이로서 데이터 0 및 3 사이의 특정 전이를 오해한 결과로서 때때로 잘못된 잠금 지점에서 잠깁니다.(도 2).

그림 2 전송 속도 CDR 회로의 잘못된 잠금 문제 ©2022 IEEE(*7)

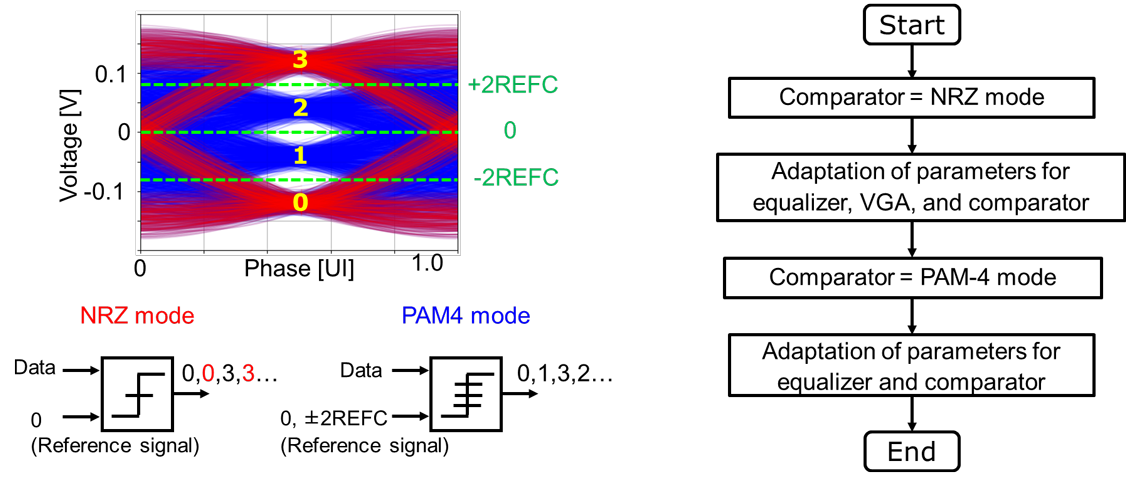

NEDO와 Kioxia는 PAM4 신호가 입력되더라도 비교기(*6)가 NRZ 모드에서 작동될 때 클럭 신호가 올바른 지점에서 잠긴다는 것을 발견했습니다. 따라서 NRZ 모드에서 비교기를 사용하면 잘못된 잠금 문제를 피할 수 있습니다. 비교기는 먼저 NRZ 모드에서 작동한 다음 이퀄라이저, 가변 이득 증폭기 및 비교기의 매개변수를 적응적으로 제어합니다. 다음으로, PAM4 입력 신호에서 클럭 신호가 성공적으로 복구됩니다. 그 후, 비교기를 PAM4 모드로 변경하고 이퀄라이저 및 비교기의 파라미터를 다시 최적화하고 클럭 신호를 적절히 조정합니다.(그림 3).

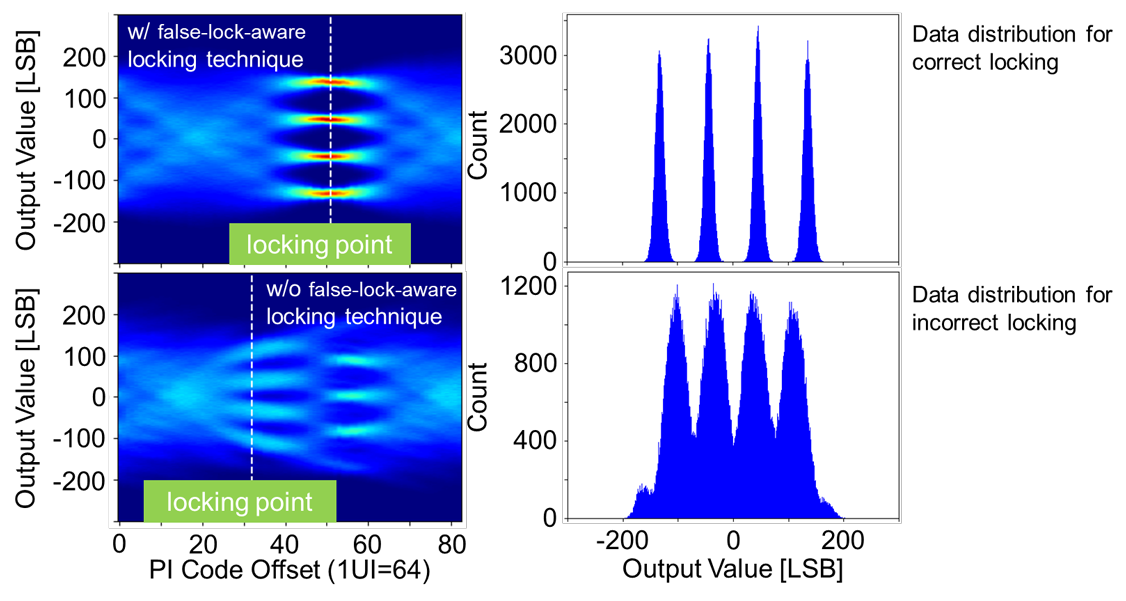

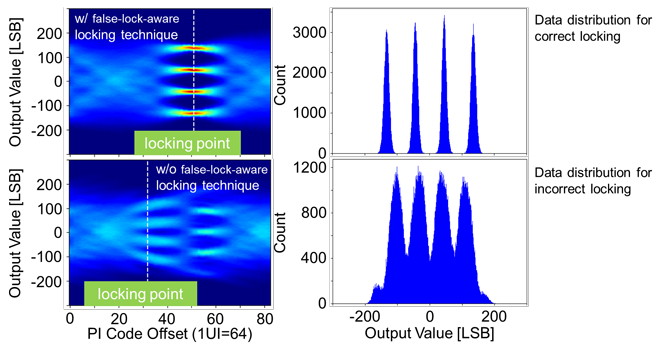

제조된 수신기를 측정할 때 56-Gbps PAM4 신호가 송신기에서 생성된 다음 외부 케이블을 통해 수신기에 입력됩니다. 제안된 false-lock-aware 잠금 기술을 사용하면 처음에는 클럭 신호가 잘못된 잠금 지점에서 잠긴 경우에도 PAM4 신호가 올바르게 수신됩니다(그림 4).

그림 3 제안된 false-lock-aware 잠금 기술

그림 4 false-lock-aware 기법에 대한 측정 결과 ©2022 IEEE (*7)

3. 향후 계획

Kioxia는 데이지 체인 트랜시버(*8)를 사용하는 고대역폭 대용량 메모리 모듈에 이 false-lock-aware 잠금 기술을 적용할 것입니다. NEDO의 프로젝트에서 40W 미만의 전력 소비, 5TB 이상의 메모리 용량 및 64GB/s 이상의 대역폭을 목표로 개발되고 있습니다.

5G MEC 서버(*9)에서 빅데이터 분석을 위해 이러한 메모리 모듈을 사용함으로써IoT와 같은 산업의 디지털화를 기대할 수 있습니다.

메모

- PAM4(4레벨 펄스 진폭 변조)

2비트 데이터를 나타내는 4가지 전압 레벨을 사용하는 데이터 전송 기술입니다. 하나의 기호에는 NRZ를 사용하여 1비트 데이터가 포함되어 있지만, 하나의 기호 전송에는 PAM4를 사용하여 2비트 데이터가 포함되어 있습니다. - NRZ(영점으로 복귀하지 않음)

"0"과 "1"을 나타내는 두 가지 전압 레벨을 사용하는 데이터 전송 기술. - 변조율

1초당 기호 변경 횟수를 기호 속도 또는 전송 속도라고도 합니다. - CDR(클럭 및 데이터 복구)

수신된 신호에서 클럭 및 데이터 신호를 복구하는 기술입니다. - 비교기

입력 전압과 기준 전압 값을 비교하는 회로입니다. - 56-Gbps PAM4 트랜시버

이 개발에서는 400GbE의 최신 이더넷 기술을 위한 56-Gbps 트랜시버를 가정합니다. - 프레젠테이션 제목

F. Tachibana et al., “Mueller-Müller CDR용 False-Lock-Aware 잠금 체계를 갖춘 56-Gb/s PAM4 트랜시버”, IEEE

유럽 Solid-State 회로 컨퍼런스 2022(ESSCIRC 2022) - 데이지 체인 트랜시버

데이지 체인 구성을 사용하여 메모리 컨트롤러와 NAND 플래시 메모리 사이에 여러 트랜시버가 연결됩니다.

고대역폭 및 대용량 메모리 모듈에 효과적입니다. - MEC 서버(Mobile Edge Computing Server)

모바일 터미널 근처에 위치한 서버는 지연 시간이 짧은 통신을 실현하는 데 효과적입니다.

- 여기에서 언급된 다른 모든 회사 이름, 제품 및 서비스 이름은 해당 회사의 상표일 수 있습니다.

Information in this document, including product prices and specifications, content of services and contact information, is correct on the date of the announcement but is subject to change without prior notice.