Please select your location and preferred language where available.

Kioxia, 고밀도 저전력 3D DRAM의 실제 구현을 가능하게 하는 핵심 기술 개발

고도로 적층 가능한 산화물 반도체 채널 트랜지스터의 기술 시연

- 2025년 12월 12일

- KIOXIA Corporation

메모리 솔루션의 세계적인 리더인 Kioxia Corporation은 오늘 고집적, 저전력 3D DRAM의 실질적인 구현을 가능하게 할 고적층 산화물 반도체 채널 트랜지스터 개발을 발표했습니다. 이 기술은 12월 10일 미국 샌프란시스코에서 열린 IEEE 국제 전자 소자 회의(IEDM)에서 발표되었으며, AI 서버 및 IoT 부품을 포함한 광범위한 애플리케이션에서 전력 소비를 줄일 수 있는 잠재력을 가지고 있습니다.

AI 시대에는 대용량 데이터를 처리할 수 있는 더 큰 용량과 더 낮은 전력 소비를 가진 DRAM에 대한 수요가 증가하고 있습니다. 기존 DRAM 기술은 메모리 셀 크기 조정의 물리적 한계에 도달하여 메모리 셀의 3D 스택에 대한 연구를 촉진하여 추가 용량을 제공합니다. 적층 메모리 셀에서 트랜지스터용 채널 재료로 단결정 실리콘을 사용하는 것은 종래의 DRAM의 경우와 같이 제조 비용을 증가시키고, 메모리 셀을 새로 고치는 데 필요한 전력은 메모리 용량에 비례하여 증가한다.

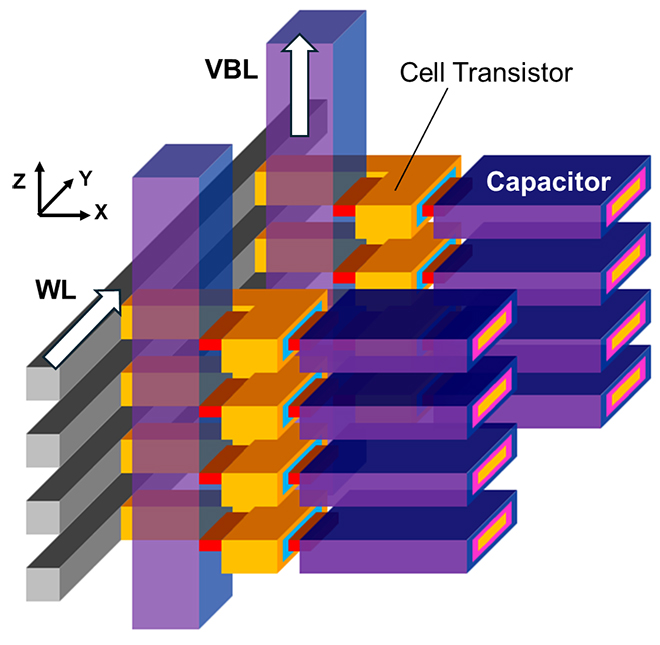

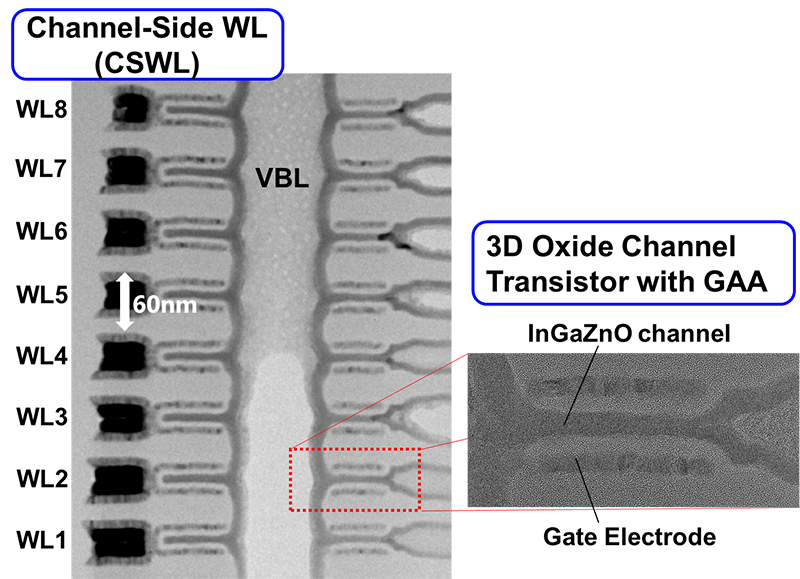

작년 IEDM에서 산화물 반도체로 만든 수직 트랜지스터를 사용하는 Oxide-Semiconductor Channel Transistor DRAM(OCTRAM) 기술의 개발을 발표했습니다. 올해 프레젠테이션에서는 OCTRAM의 3D 적층을 가능하게 하는 고도로 적층 가능한 산화물 반도체 채널 트랜지스터 기술을 선보였으며, 이는 8개 레이어로 적층된 트랜지스터의 작동을 검증합니다.

이 새로운 기술은 성숙한 실리콘 산화물 및 실리콘 질화물 막을 적층하고 실리콘 질화물 영역을 산화물 반도체(InGaZnO)로 대체하여 수평 적층 트랜지스터의 수직 층을 동시에 형성한다. 또한 수직 피치를 확장할 수 있는 새로운 3D 메모리 셀 구조를 도입했습니다. 이러한 제조 공정 및 구조는 메모리 셀의 3D 적층을 달성하는 비용 문제를 극복할 것으로 예상된다.

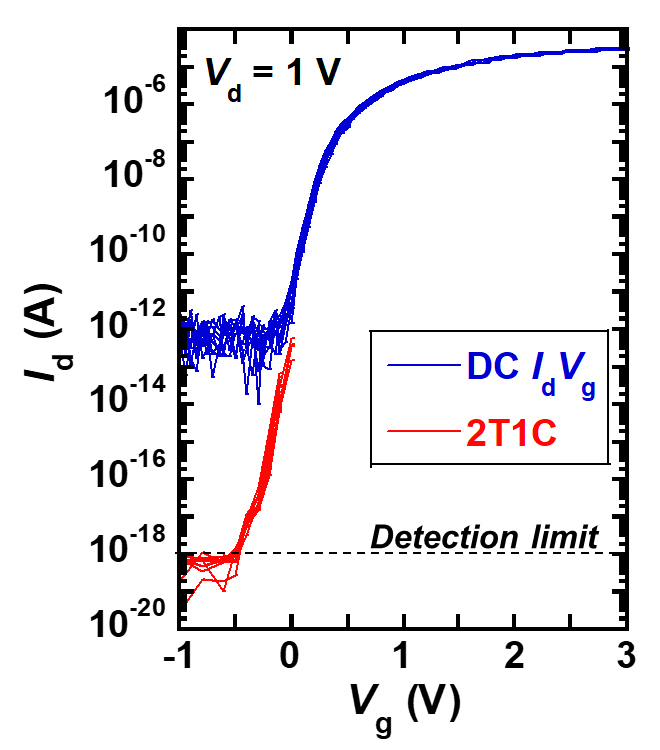

또한, 산화물 반도체의 낮은 오프-전류 특성으로 인해 리프레시 전력이 감소될 수 있을 것으로 예상된다. 당사는 교체 공정에 의해 형성된 수평 트랜지스터에 대해 높은 온전류(이상 30μA) 및 초저 오프 전류(이상 1aA, 10^-18A) 기능을 입증했습니다. 또한 수평 트랜지스터의 8층 스택을 성공적으로 제작하고 해당 구조 내에서 트랜지스터의 성공적인 작동을 확인했습니다.

Kioxia Corporation은 실제 응용 분야에서 3D DRAM의 배치를 실현하기 위해 이 기술의 연구 개발을 계속할 것입니다.

- This announcement has been prepared to provide information on our business and does not constitute or form part of an offer or invitation to sell or a solicitation of an offer to buy or subscribe for or otherwise acquire any securities in any jurisdiction or an inducement to engage in investment activity nor shall it form the basis of or be relied on in connection with any contract thereof.

- Information in this document, including product prices and specifications, content of services and contact information, is correct on the date of the announcement but is subject to change without prior notice.